# **EDA Simulator Link™ DS 2** User's Guide

### How to Contact The MathWorks

www.mathworks.com Web

comp.soft-sys.matlab Newsgroup

www.mathworks.com/contact\_TS.html Technical Support

(a)

${\tt suggest@mathworks.com} \qquad \qquad {\tt Product\ enhancement\ suggestions}$

bugs@mathworks.com

Bug reports

doc@mathworks.com

Documentation error reports

service@mathworks.com Order status, license renewals, passcodes info@mathworks.com Sales, pricing, and general information

E00 C47 70

508-647-7000 (Phone)

508-647-7001 (Fax)

The MathWorks, Inc. 3 Apple Hill Drive Natick, MA 01760-2098

For contact information about worldwide offices, see the MathWorks Web site.

EDA Simulator Link™ DS User's Guide

© COPYRIGHT 2008–2009 by The MathWorks, Inc.

The software described in this document is furnished under a license agreement. The software may be used or copied only under the terms of the license agreement. No part of this manual may be photocopied or reproduced in any form without prior written consent from The MathWorks, Inc.

FEDERAL ACQUISITION: This provision applies to all acquisitions of the Program and Documentation by, for, or through the federal government of the United States. By accepting delivery of the Program or Documentation, the government hereby agrees that this software or documentation qualifies as commercial computer software or commercial computer software documentation as such terms are used or defined in FAR 12.212, DFARS Part 227.72, and DFARS 252.227-7014. Accordingly, the terms and conditions of this Agreement and only those rights specified in this Agreement, shall pertain to and govern the use, modification, reproduction, release, performance, display, and disclosure of the Program and Documentation by the federal government (or other entity acquiring for or through the federal government) and shall supersede any conflicting contractual terms or conditions. If this License fails to meet the government's needs or is inconsistent in any respect with federal procurement law, the government agrees to return the Program and Documentation, unused, to The MathWorks, Inc.

### **Trademarks**

MATLAB and Simulink are registered trademarks of The MathWorks, Inc. See www.mathworks.com/trademarks for a list of additional trademarks. Other product or brand names may be trademarks or registered trademarks of their respective holders.

### Patent

The MathWorks products are protected by one or more U.S. patents. Please see www.mathworks.com/patents for more information.

### **Revision History**

| March 2008   | Online only | New for Version 1 (Release 2008a)       |

|--------------|-------------|-----------------------------------------|

| October 2008 | Online only | Updated for Version 2.0 (Release 2008b) |

| March 2009   | Online only | Updated for Version 2.1 (Release 2009a) |

## **Getting Started**

| 4 | ı |  |  |

|---|---|--|--|

| ı |   |  |  |

|   |   |  |  |

|   |   |  |  |

|   |   |  |  |

|   |   |  |  |

| Product Overview                                                                                 | 1-2  |

|--------------------------------------------------------------------------------------------------|------|

| Integration with Other Products                                                                  | 1-2  |

| Hardware Description Language (HDL) Support                                                      | 1-4  |

| Linking with MATLAB and the HDL Simulator                                                        | 1-4  |

| Linking with Simulink and the HDL Simulator<br>Communicating with MATLAB or Simulink and the HDL | 1-7  |

| Simulator                                                                                        | 1-8  |

| Requirements                                                                                     | 1-9  |

| What You Need to Know                                                                            | 1-9  |

| Required Products                                                                                | 1-9  |

| Setting Up Your Environment for the EDA Simulator                                                |      |

| Link DS Software                                                                                 | 1-11 |

| Installing the Link Software                                                                     | 1-11 |

| Installing Related Application Software                                                          | 1-11 |

| Using the EDA Simulator Link DS Libraries                                                        | 1-11 |

| Starting the HDL Simulator                                                                       | 1-15 |

| Starting the HDL Simulator from MATLAB                                                           | 1-15 |

| Starting the Synopsys VCS MX Software from a Shell                                               | 1-16 |

| Learning More About the EDA Simulator Link DS                                                    |      |

| Software                                                                                         | 1-17 |

| Documentation Overview                                                                           | 1-17 |

| Online Help                                                                                      | 1-18 |

| Demos and Tutorials                                                                              | 1-19 |

### Simulating an HDL Component in a MATLAB Test Bench Environment

|   | • |

|---|---|

|   |   |

| 4 |   |

|   |   |

| Workflow for Simulating an HDL Component with a MATLAB Test Bench Function                  |                           |  |

|---------------------------------------------------------------------------------------------|---------------------------|--|

| Overview to Using MATLAB as a Test Bench                                                    | 2-5                       |  |

| Code HDL Modules for Verification Using MATLAB  Overview to Coding HDL Modules for Use with | 2-7                       |  |

| MATLAB                                                                                      | 2-7                       |  |

| Choosing an HDL Module Name  Specifying Port Direction Modes in HDL Components              | 2-7                       |  |

| (MATLAB as Test Bench)                                                                      | 2-8<br>2-8                |  |

| Sample VHDL Entity Definition                                                               | 2-10                      |  |

| Compiling and Debugging the HDL Model                                                       | 2-10                      |  |

| Code an EDA Simulator Link DS MATLAB Test Bench                                             |                           |  |

| Function                                                                                    | 2-11                      |  |

| Functions                                                                                   | 2-11                      |  |

| Syntax of a Test Bench Function                                                             | 2-12                      |  |

| Sample MATLAB Test Bench Function                                                           | 2-12                      |  |

| Place Test Bench Function on MATLAB Search Path                                             | 2-20                      |  |

| Start hdldaemon to Provide Connection to HDL                                                |                           |  |

| Simulator                                                                                   | 2-21                      |  |

| Launch HDL Simulator for Use with MATLAB                                                    | 2-28                      |  |

| Launching the HDL Simulator                                                                 | 2-28                      |  |

| Loading an HDL Design for Verification                                                      | 2-23                      |  |

| Invoke matlabtb to Bind and Schedule MATLAB Test                                            | 2.2                       |  |

| Bench Function Calls                                                                        | <b>2-2</b> 4 <b>2-2</b> 4 |  |

| Invoking matlabth                                                                           | Z-Z4                      |  |

| Bench Function                                                                                                                                                                                                                                               | 2-26<br>2-26             |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------|

| Run MATLAB Test Bench Simulation                                                                                                                                                                                                                             | 2-29<br>2-29<br>2-29     |

| Running a Test Bench Cosimulation                                                                                                                                                                                                                            | 2-30                     |

| Command                                                                                                                                                                                                                                                      | 2-31<br>2-32             |

| Stop Test Bench Simulation                                                                                                                                                                                                                                   | 2-33                     |

| <br>Replacing an HDL Component with a MATI<br>Component Func                                                                                                                                                                                                 |                          |

|                                                                                                                                                                                                                                                              |                          |

| Workflow for Creating a MATLAB Component Function for Use with the HDL Simulator  Overview to Using a MATLAB Function as a Component                                                                                                                         | 3-2<br>3-5               |

| for Use with the HDL Simulator  Overview to Using a MATLAB Function as a                                                                                                                                                                                     |                          |

| for Use with the HDL Simulator                                                                                                                                                                                                                               | 3-5                      |

| for Use with the HDL Simulator  Overview to Using a MATLAB Function as a Component  Code HDL Modules for Visualization Using MATLAB  Code an EDA Simulator Link DS MATLAB Component Function                                                                 | 3-5<br>3-7               |

| for Use with the HDL Simulator  Overview to Using a MATLAB Function as a Component  Code HDL Modules for Visualization Using MATLAB  Code an EDA Simulator Link DS MATLAB Component Function  Overview to Coding an EDA Simulator Link DS Component Function | 3-5<br>3-7<br>3-8<br>3-8 |

| Start HDL Simulator for Use with MATLAB                                                                                                   |           |

|-------------------------------------------------------------------------------------------------------------------------------------------|-----------|

| Invoke matlabcp to Bind and Schedule MATLAB Component Function Calls                                                                      |           |

| Run MATLAB Component Simulation                                                                                                           |           |

| Simulating an HDL Component in a Si<br>Test Bench Enviro                                                                                  | mı<br>oni |

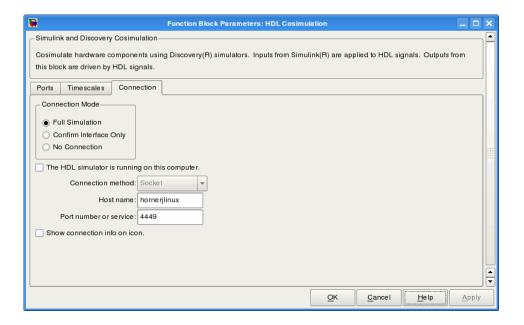

| Workflow for Simulating an HDL Component in a Simulink Test Bench Environment                                                             |           |

| Overview to Using Simulink as a Test Bench Understanding How the HDL Simulator and Simulink Software Communicate Using EDA Simulator Link |           |

| DS                                                                                                                                        |           |

| Create a Simulink Model for Test Bench Cosimulation with the HDL Simulator                                                                | <br>      |

| Adding a Value Change Dump (VCD) File (Optional) .  Code an HDL Component for Use with Simulink Tes Bench Applications                    | st        |

| Overview to Coding HDL Components for Use with Simulink                                                                                   |           |

| Launch HDL Simulator for Test Bench Cosimulation with Simulink                                                                            |           |

| Add the HDL Cosimulation Block to the Simulink Test                                                |             |

|----------------------------------------------------------------------------------------------------|-------------|

| Bench Model                                                                                        | 4-12        |

| Define the HDL Cosimulation Block Interface (Simulink                                              |             |

| as Test Bench)                                                                                     | 4-13        |

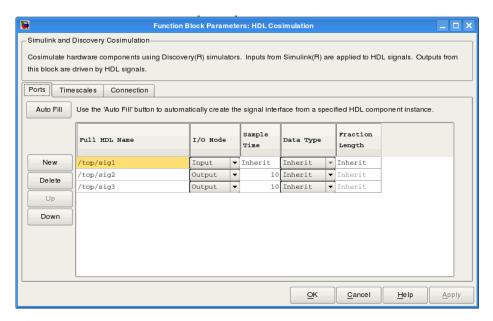

| Accessing the HDL Cosimulation Block Interface                                                     | 4-13        |

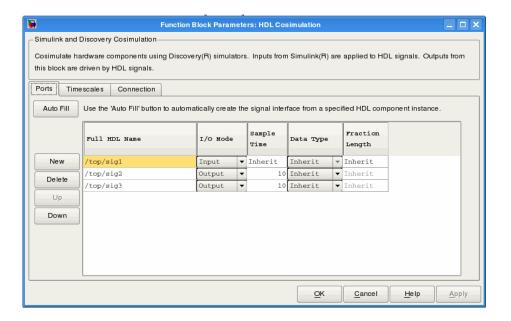

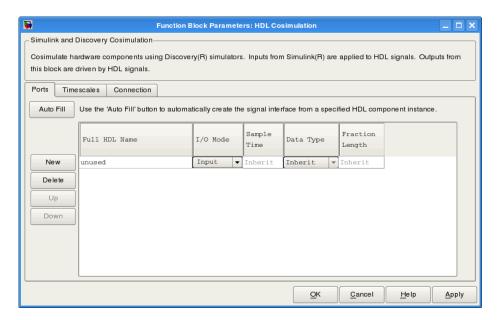

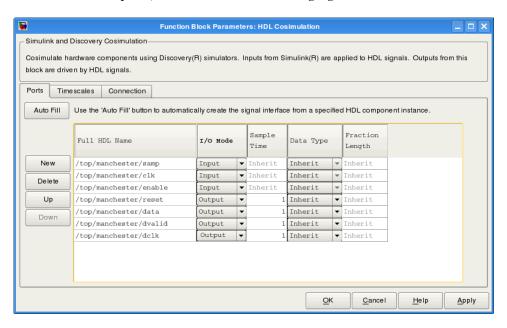

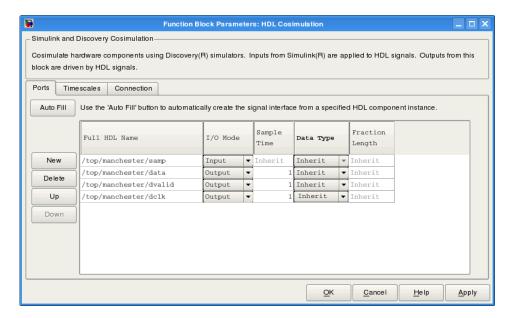

| Mapping HDL Signals to Block Ports                                                                 | 4-14        |

| Specifying the Signal Data Types                                                                   | 4-24        |

| Configuring the Simulink and HDL Simulator Timing                                                  |             |

| Relationship                                                                                       | 4-24        |

| Configuring the Communication Link in the HDL                                                      |             |

| Cosimulation Block                                                                                 | 4-27        |

| Programmatically Controlling the Block Parameters                                                  | 4-30        |

| Start the HDL Simulation                                                                           | 4-33        |

| Run a Test Bench Cosimulation Session (Simulink as                                                 |             |

| Test Bench)                                                                                        | 4-34        |

| Setting Simulink Software Configuration Parameters                                                 | 4-34        |

| Determining an Available Socket Port Number                                                        | 4-36        |

| Checking the Connection Status                                                                     | 4-36        |

| Running and Testing a Cosimulation Model                                                           | 4-36        |

| Avoiding Race Conditions in HDL Simulation When<br>Cosimulating With the EDA Simulator Link DS HDL |             |

| Cosimulation Block                                                                                 | 4-36        |

| Replacing an HDL Component with a Simul<br>Algori                                                  | link<br>thm |

| Workflow for Using Simulink as HDL Component                                                       | 5-2         |

| Oit- Common and Simulation with Simulial                                                           | F 4         |

| Overview to Component Simulation with Simulink  How the HDL Simulator and Simulink Software        | 5-4         |

| Communicate Using EDA Simulator Link DS                                                            | 5-4         |

| Creating the HDL Module                                                                            | 5-5         |

|                                                                                                    |             |

| Introduction to the EDA Simulator Link DS HDL                                                      | • •         |

| Introduction to the EDA Simulator Link DS HDL<br>Cosimulation Block (Simulink as Component)        | 5-6         |

| Applications                                                                                                 | 5-7          |

|--------------------------------------------------------------------------------------------------------------|--------------|

| Create Simulink Model for Component Cosimulation with the HDL Simulator                                      | 5-8          |

| Launch HDL Simulator for Component Cosimulation with Simulink                                                | 5-9          |

| Add the HDL Cosimulation Block to the Simulink Component Model                                               | 5-10         |

| Define the HDL Cosimulation Block Interface                                                                  | 5-11         |

| Start the Simulation in Simulink                                                                             | 5-12         |

| Run a Component Cosimulation Session                                                                         | <b>5-1</b> 3 |

|                                                                                                              |              |

| Recording Simulink Signal State Transiti<br>for Post-Process                                                 | ons          |

| Recording Simulink Signal State Transiti for Post-Process  Adding a Value Change Dump (VCD) File             | ions<br>sing |

| for Post-Process                                                                                             | 6-2          |

| for Post-Process  Adding a Value Change Dump (VCD) File                                                      | 6-2          |

| Additional Deployment Opti  Performing Cross-Network Cosimulation Introduction to Cross-Network Cosimulation | 6-2          |

| Additional Deployment Opti  Performing Cross-Network Cosimulation                                            | 6-2<br>ions  |

| Simulator and Simulink                                                                                                                                                                                                                                                                                                                                                                                                                                       |          |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|

| Establishing EDA Simulator Link DS Machine                                                                                                                                                                                                                                                                                                                                                                                                                   |          |

| Configuration Requirements                                                                                                                                                                                                                                                                                                                                                                                                                                   |          |

| Valid Configurations For Using the EDA Simulator Lin                                                                                                                                                                                                                                                                                                                                                                                                         |          |

| DS Software with MATLAB Applications Valid Configurations For Using the EDA Simulator Lin                                                                                                                                                                                                                                                                                                                                                                    |          |

| DS Software with Simulink Software                                                                                                                                                                                                                                                                                                                                                                                                                           |          |

| Do bottware with billianik bottware                                                                                                                                                                                                                                                                                                                                                                                                                          | • • •    |

| Specifying TCP/IP Socket Communication                                                                                                                                                                                                                                                                                                                                                                                                                       | 7        |

| Choosing TCP/IP Socket Ports                                                                                                                                                                                                                                                                                                                                                                                                                                 | 7        |

| Specifying TCP/IP Values                                                                                                                                                                                                                                                                                                                                                                                                                                     | 7        |

| TCP/IP Services                                                                                                                                                                                                                                                                                                                                                                                                                                              | 7        |

| Improving Simulation Speed                                                                                                                                                                                                                                                                                                                                                                                                                                   | 7        |

| Obtaining Baseline Performance Numbers                                                                                                                                                                                                                                                                                                                                                                                                                       |          |

| Analyzing Simulation Performance                                                                                                                                                                                                                                                                                                                                                                                                                             |          |

| Cosimulating Frame-Based Signals with Simulink                                                                                                                                                                                                                                                                                                                                                                                                               |          |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                              |          |

| Advanced Operational                                                                                                                                                                                                                                                                                                                                                                                                                                         |          |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                              |          |

| Advanced Operational  Avoiding Race Conditions in HDL Simulators                                                                                                                                                                                                                                                                                                                                                                                             | Topi     |

| Advanced Operational  Avoiding Race Conditions in HDL Simulators  Overview to Avoiding Race Conditions                                                                                                                                                                                                                                                                                                                                                       | Topi     |

| Advanced Operational  Avoiding Race Conditions in HDL Simulators  Overview to Avoiding Race Conditions                                                                                                                                                                                                                                                                                                                                                       |          |

| Advanced Operational  Avoiding Race Conditions in HDL Simulators  Overview to Avoiding Race Conditions                                                                                                                                                                                                                                                                                                                                                       |          |

| Advanced Operational  Avoiding Race Conditions in HDL Simulators  Overview to Avoiding Race Conditions                                                                                                                                                                                                                                                                                                                                                       |          |

| Advanced Operational  Avoiding Race Conditions in HDL Simulators  Overview to Avoiding Race Conditions                                                                                                                                                                                                                                                                                                                                                       | <br>     |

| Advanced Operational  Avoiding Race Conditions in HDL Simulators  Overview to Avoiding Race Conditions  Potential Race Conditions in Simulink Link Sessions .  Potential Race Conditions in MATLAB Link Sessions .  Further Reading                                                                                                                                                                                                                          |          |

| Advanced Operational  Avoiding Race Conditions in HDL Simulators Overview to Avoiding Race Conditions Potential Race Conditions in Simulink Link Sessions Potential Race Conditions in MATLAB Link Sessions Further Reading  Performing Data Type Conversions Converting HDL Data to Send to MATLAB Array Indexing Differences Between MATLAB and                                                                                                            | <br><br> |

| Advanced Operational  Avoiding Race Conditions in HDL Simulators Overview to Avoiding Race Conditions Potential Race Conditions in Simulink Link Sessions Potential Race Conditions in MATLAB Link Sessions Further Reading  Performing Data Type Conversions Converting HDL Data to Send to MATLAB Array Indexing Differences Between MATLAB and HDL                                                                                                        |          |

| Advanced Operational  Avoiding Race Conditions in HDL Simulators Overview to Avoiding Race Conditions Potential Race Conditions in Simulink Link Sessions Potential Race Conditions in MATLAB Link Sessions Further Reading  Performing Data Type Conversions Converting HDL Data to Send to MATLAB Array Indexing Differences Between MATLAB and HDL Converting Data for Manipulation                                                                       |          |

| Advanced Operational  Avoiding Race Conditions in HDL Simulators Overview to Avoiding Race Conditions Potential Race Conditions in Simulink Link Sessions Potential Race Conditions in MATLAB Link Sessions Further Reading  Performing Data Type Conversions Converting HDL Data to Send to MATLAB Array Indexing Differences Between MATLAB and HDL                                                                                                        |          |

| Avoiding Race Conditions in HDL Simulators Overview to Avoiding Race Conditions Potential Race Conditions in Simulink Link Sessions Potential Race Conditions in MATLAB Link Sessions Further Reading  Performing Data Type Conversions Converting HDL Data to Send to MATLAB Array Indexing Differences Between MATLAB and HDL Converting Data for Manipulation Converting Data for Return to the HDL Simulator  Understanding How Simulink Software Drives |          |

| Avoiding Race Conditions in HDL Simulators Overview to Avoiding Race Conditions Potential Race Conditions in Simulink Link Sessions Potential Race Conditions in MATLAB Link Sessions Further Reading  Performing Data Type Conversions Converting HDL Data to Send to MATLAB Array Indexing Differences Between MATLAB and HDL Converting Data for Manipulation Converting Data for Return to the HDL Simulator                                             |          |

| Understanding the Representation of Simulation                                                    |      |

|---------------------------------------------------------------------------------------------------|------|

| Time                                                                                              | 8-15 |

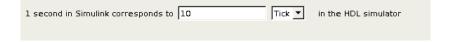

| Overview to the Representation of Simulation Time  Defining the Simulink and HDL Simulator Timing | 8-15 |

| Relationship                                                                                      | 8-16 |

| Setting the Timing Mode with EDA Simulator Link DS                                                | 8-16 |

| Relative Timing Mode                                                                              | 8-17 |

| Absolute Timing Mode                                                                              | 8-19 |

| Timing Mode Usage Considerations                                                                  | 8-21 |

| Setting HDL Cosimulation Port Sample Times                                                        | 8-22 |

| Handling Multirate Signals                                                                        | 8-24 |

| Understanding Block Simulation Latency                                                            | 8-25 |

| Overview to Block Simulation Latency                                                              | 8-25 |

| Interfacing with Continuous Time Signals                                                          | 8-27 |

| M-Function Prototype Refere                                                                       | nce  |

|                                                                                                   |      |

| Defining EDA Simulator Link DS M-Functions and                                                    |      |

| Function Parameters                                                                               | 9-2  |

| M-Function Syntax and Function Argument Definitions                                               | 9-2  |

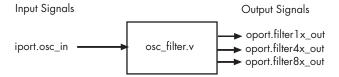

| Oscfilter Function Example                                                                        | 9-4  |

| Gaining Access to and Applying Port Information                                                   | 9-5  |

| Scheduling EDA Simulator Link DS M-Functions Using                                                |      |

| the tnext Parameter                                                                               | 9-8  |

| 10 | Functions — Alphabetical List                           |

|----|---------------------------------------------------------|

| 11 | HDL Simulator Command Extensions —<br>Alphabetical List |

|    | Blocks — Alphabetical List                              |

| 12 |                                                         |

|    | Index                                                   |

# Getting Started

- "Product Overview" on page 1-2

- "Requirements" on page 1-9

- "Setting Up Your Environment for the EDA Simulator Link DS Software" on page 1-11

- $\bullet\,$  "Starting the HDL Simulator" on page 1-15

- "Learning More About the EDA Simulator Link DS Software" on page 1-17

### **Product Overview**

### In this section...

"Integration with Other Products" on page 1-2

"Hardware Description Language (HDL) Support" on page 1-4

"Linking with MATLAB and the HDL Simulator" on page 1-4

"Linking with Simulink and the HDL Simulator" on page 1-7

"Communicating with MATLAB or Simulink and the HDL Simulator" on page 1-8

### **Integration with Other Products**

The EDA Simulator Link<sup>TM</sup> DS cosimulation interface integrates MathWorks<sup>TM</sup> tools into the Electronic Design Automation (EDA) workflow. This integration enhances capabilities for field programmable gate array (FPGA) and application-specific integrated circuit (ASIC) development. The software provides a bidirectional link between the Synopsys hardware description language (HDL) simulator, Synopsys VCS<sup>TM</sup> MX, and The MathWorks<sup>TM</sup> MATLAB® and Simulink® products. Such linking makes direct hardware design verification and cosimulation possible. The integration of these tools allows users to apply each product to the tasks it does best:

- Synopsys VCS MX Hardware modeling in HDL and simulation

- MATLAB Numerical computing, algorithm development, and visualization

- Simulink Simulation of system-level designs and complex models

**Note** Synopsys VCS MX software may also be referred to as *the HDL simulator* throughout this document.

The EDA Simulator Link DS software consists of MATLAB functions and HDL simulator commands that establish communication links between the HDL simulator and The MathWorks products. In addition, the link software

contains a library of Simulink blocks that you may use to include HDL simulator designs in Simulink models for cosimulation.

EDA Simulator Link DS software streamlines FPGA and ASIC development by integrating tools available for these processes:

- 1 Developing specifications for hardware design reference models

- 2 Implementing a hardware design in HDL based on a reference model

- **3** Verifying the design against the reference design

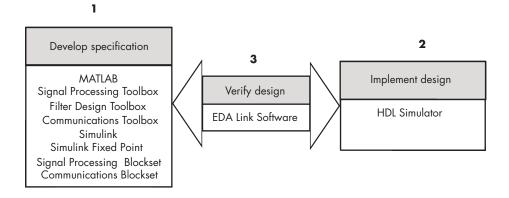

The following figure shows how the HDL simulator and MathWorks products fit into this hardware design scenario.

As the figure shows, EDA Simulator Link DS software connects tools that traditionally have been used discretely to perform specific steps in the design process. By connecting these tools, the link simplifies verification by allowing you to cosimulate the implementation and original specification directly. This cosimulation results in significant time savings and the elimination of errors inherent to manual comparison and inspection.

In addition to the preceding design scenario, EDA Simulator Link DS software enables you to work with tools in the following ways:

- Use MATLAB or Simulink to create test signals and software test benches for HDL code

- Use MATLAB or Simulink to provide a behavioral model for an HDL simulation

- Use MATLAB analysis and visualization capabilities for real-time insight into an HDL implementation

- Use Simulink to translate legacy HDL descriptions into system-level views

**Note** You can cosimulate a module using SystemVerilog, SystemC or both with MATLAB or Simulink using the EDA Simulator Link DS software. Write simple wrappers around the SystemC and make sure that the SystemVerilog cosimulation connections are to ports or signals of data types supported by the link cosimulation interface.

### Hardware Description Language (HDL) Support

All EDA Simulator Link DS MATLAB functions and the HDL Cosimulation block offer the same language-transparent feature set for both Verilog and VHDL models.

EDA Simulator Link DS software also supports mixed-language HDL models (models with both Verilog and VHDL components), allowing you to cosimulate VHDL and Verilog signals simultaneously. Both MATLAB and Simulink software can access components in different languages at any level.

### Linking with MATLAB and the HDL Simulator

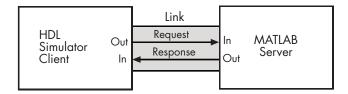

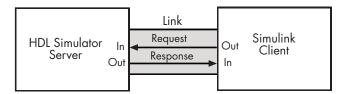

When linked with MATLAB, the HDL simulator functions as the client, as the following figure shows.

In this scenario, a MATLAB server function waits for service requests that it receives from an HDL simulator session. After receiving a request, the server establishes a communication link and invokes a specified MATLAB function that computes data for, verifies, or visualizes the HDL module (coded in VHDL or Verilog) that is under simulation in the HDL simulator.

After the server is running, you can start and configure the HDL simulator or use with MATLAB with the supplied EDA Simulator Link DS function launchDiscovery. Required and optional parameters allow you to specify the following:

- Tcl commands that execute as part of startup

- A specific Synopsys VCS MX executable to start

- The name of a VCS startup file to store the complete startup script for future use or reference

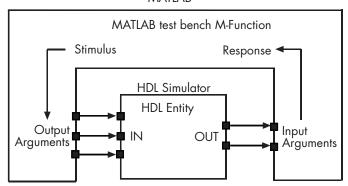

The following figure shows how a MATLAB test bench function wraps around and communicates with the HDL simulator during a test bench simulation session.

### **MATLAB**

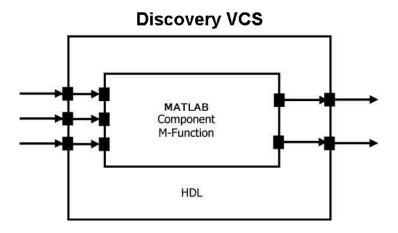

The following figure shows how a MATLAB component function is wrapped around by and communicates with the HDL simulator during a component simulation session.

# MATLAB Component M-Function HDL

During the configuration process, EDA Simulator Link DS software equips the HDL simulator with a set of customized command extensions you use to perform the following tasks:

- Load the HDL simulator with an instance of an HDL module to be tested with MATLAB

- Begin a MATLAB test bench or component session for that instance

When you begin a specific test bench session, you specify parameters that identify the following information:

- The mode and, if appropriate, TCP/IP data necessary for connecting to a MATLAB server

- The MATLAB function that is associated with and executes on behalf of the HDL instance

- Timing specifications and other control data that specifies when the module's MATLAB function is to be called

### Linking with Simulink and the HDL Simulator

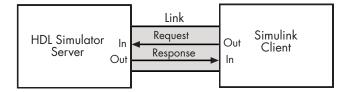

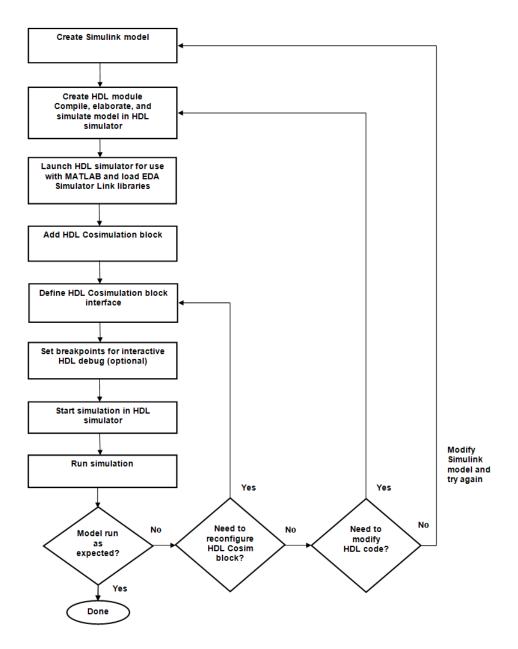

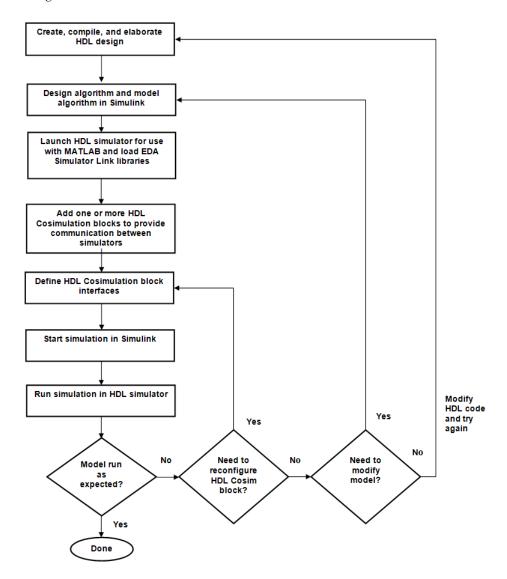

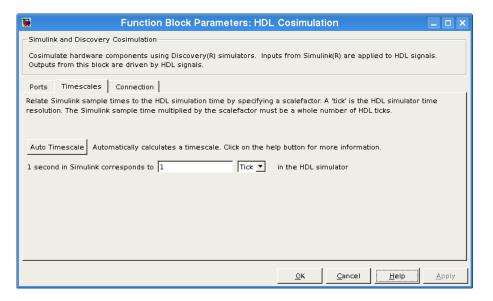

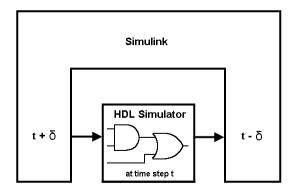

When linked with Simulink, the HDL simulator functions as the server, as shown in the following figure.

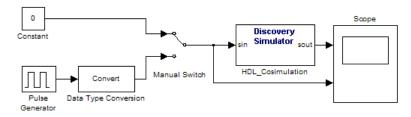

In this case, the HDL simulator responds to simulation requests it receives from cosimulation blocks in a Simulink model. You begin a cosimulation session from Simulink. After a session is started, you can use Simulink and the HDL simulator to monitor simulation progress and results. For example, you might add signals to an HDL simulator Wave window to monitor simulation timing diagrams.

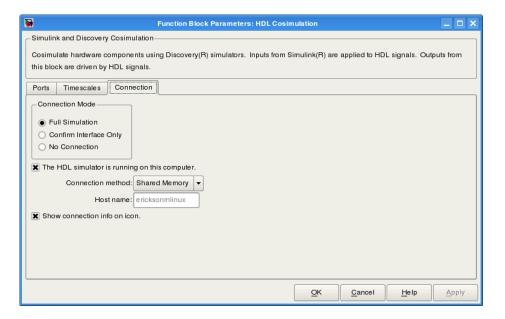

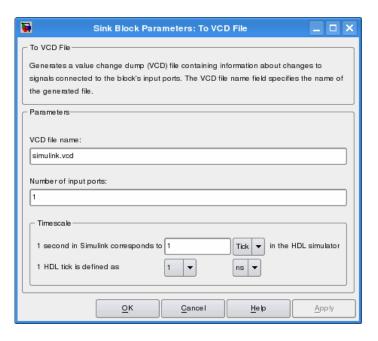

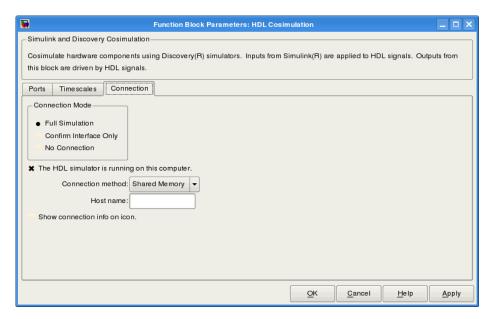

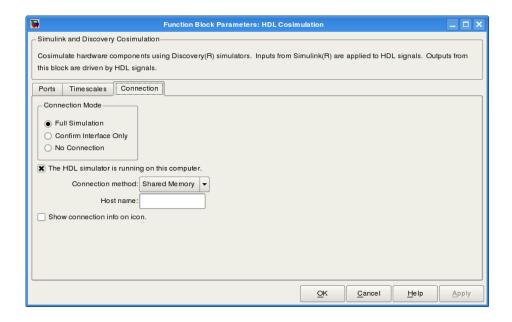

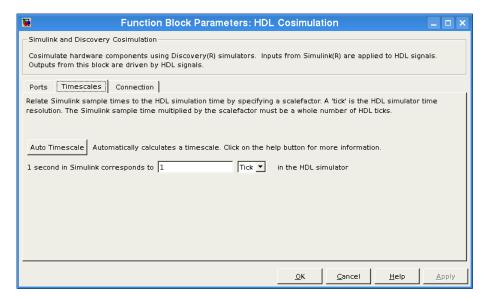

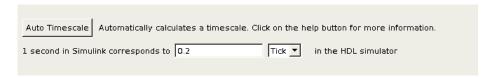

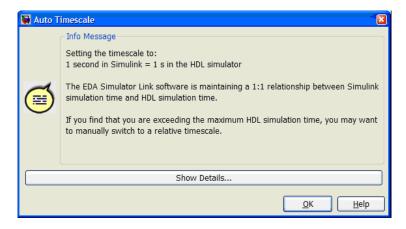

Using the Block Parameters dialog box for an HDL Cosimulation block, you can configure the following:

Block input and output ports that correspond to signals (including internal signals) of an HDL module. You can specify sample times and fixed-point data types for individual block output ports if desired.  Type of communication and communication settings used for exchanging data between the simulation tools.

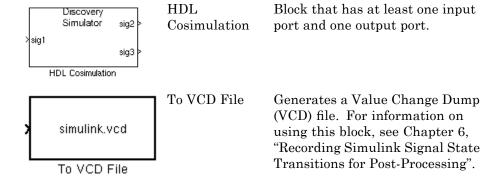

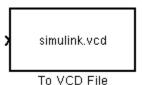

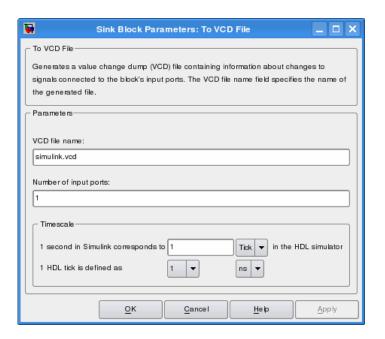

EDA Simulator Link DS software also includes a block for generating value change dump (VCD) files. You can use VCD files generated with this block to perform the following tasks:

- View Simulink simulation waveforms in your HDL simulation environment

- Compare results of multiple simulation runs, using the same or different simulation environments

- Use as input to post-simulation analysis tools

# Communicating with MATLAB or Simulink and the HDL Simulator

The mode of communication that you use for a link between the HDL simulator and MATLAB or Simulink depends on whether your simulation application runs in a local, single-system configuration or in a network configuration. If the HDL simulator and The MathWorks products can run locally on the same system and your application requires only one communication channel, you have the option of choosing between shared memory and TCP/IP socket communication. Shared memory communication provides optimal performance and is the default mode of communication.

TCP/IP socket mode is more versatile. You can use it for single-system and network configurations. This option offers the greatest scalability. For more on TCP/IP socket communication, see "Specifying TCP/IP Socket Communication" on page 7-11.

### Requirements

### In this section...

"What You Need to Know" on page 1-9

"Required Products" on page 1-9

### What You Need to Know

The documentation provided with the EDA Simulator Link DS software assumes users have a moderate level of prerequisite knowledge in the following subject areas:

- Hardware design and system integration

- VHDL and/or Verilog

- Synopsys VCS MX simulators

- MATLAB

Experience with Simulink and Simulink Fixed Point software is required for applying the Simulink component of the product.

Depending on your application, experience with the following MATLAB toolboxes and Simulink blocksets might also be useful:

- Signal Processing Toolbox<sup>TM</sup>

- Filter Design Toolbox $^{TM}$

- Communications Toolbox<sup>TM</sup>

- Signal Processing Blockset<sup>TM</sup>

- Communications Blockset<sup>TM</sup>

- $\bullet~$  Video and Image Processing Blockset  $^{TM}$

### **Required Products**

EDA Simulator Link DS software requires the following:

Platform Visit the EDA Simulator Link DS

requirements page on The MathWorks Web site for specific platforms supported

with the current release.

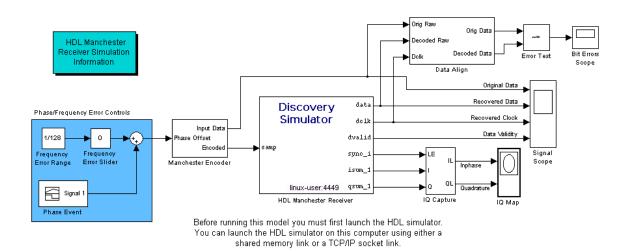

**Application software** Requires Synopsys<sup>®</sup> Discovery<sup>TM</sup> family of

simulators

Visit the EDA Simulator Link DS requirements page on The MathWorks Web site for specific versions supported

with the current release.

**MATLAB**

Application software required for cosimulation

Simulink

Simulink Fixed Point

Fixed-Point Toolbox

Optional application software

Communications Blockset

Signal Processing Blockset

Filter Design Toolbox

Signal Processing Toolbox

Video and Image Processing Blockset

**Note** Many EDA Simulator Link DS demos require one or more of the optional products listed.

Platform-specific software

The EDA Simulator Link DS shared libraries (liblfdhdls\*.so, liblfdhdlc\*.so) are built using the GCCs included in the Synopsys 2008.03 VG\_GNU\_PACKAGE distribution. To ensure compatibility with our product you must use one of these GCCs to compile your HDL.

# Setting Up Your Environment for the EDA Simulator Link DS Software

### In this section...

"Installing the Link Software" on page 1-11

"Installing Related Application Software" on page 1-11

"Using the EDA Simulator Link DS Libraries" on page 1-11

### **Installing the Link Software**

For details on how to install the EDA Simulator Link DS software, see the MATLAB installation instructions.

### **Installing Related Application Software**

Based on your configuration decisions and the software required for your EDA Simulator Link DS application, identify software you need to install and where you need to install it. For example, if you need to run multiple instances of the link MATLAB server on different machines, you need to install MATLAB and any applicable toolbox software on multiple systems. Each instance of MATLAB can run only one instance of the server.

For details on how to install the HDL simulator, see the installation instructions for that product. For information on installing and activating MathWorks products, see the MATLAB installation and activation instructions.

**Note** In addition to making sure Synopsys VCS MX is installed and on the path, you must also download and install one of the two supported GCCs in the Synopsys 2008.03 VG\_GNU\_PACKAGE release: gcc336 or gcc412. See "Using the EDA Simulator Link DS Libraries" on page 1-11.

### **Using the EDA Simulator Link DS Libraries**

In general, you want to use the same compiler for all libraries linked into the same executable. The link software provides many versions of the same library compilers that are available with the HDL simulators (usually some version of GCC). Using the same libraries ensures compatibility with other C++ libraries that may get linked into the HDL simulator, including SystemC libraries.

If you have any of these conditions, choose the version of the EDA Simulator Link DS library that matches the compiler used for that code:

- Link other third-party applications into your HDL simulator.

- Compile and link in SystemC code as part of your design or testbench.

- Write custom C/C++ applications and link them into your HDL simulator.

If you do not link any other code into your HDL simulator, you can use any version of the supplied libraries matching your installed version of GCC from the VG\_GNU\_PACKAGE. The MATLAB launchDiscovery command chooses a default version of this library.

For examples on specifying EDA Simulator Link DS libraries when cosimulating across a network, see "Performing Cross-Network Cosimulation" on page 7-2.

### **Library Names**

The EDA Simulator Link DS HDL libraries use the following naming format:

```

productdir/arch/lib{product_short_name}{client_server_tag}_{design_language}

_{compiler_tag).{libext}

```

### where

productdir discovery

arch linux32, linux64 product short name lfdhdl

client\_server\_tag c or s (MATLAB or Simulink)

$\label{eq:mixed} \texttt{design\_language} \qquad \qquad \texttt{mixed} = \texttt{pure vhdl or mixed vhdl/vlog}$

vlog = pure vlog

```

\begin{array}{ll} \texttt{compiler\_tag} & \texttt{gcc336},\,\texttt{gcc412} \\ \texttt{libext} & \texttt{so} \end{array}

```

Not all combinations are supported. See "Default Libraries" on page 1-13 for valid combinations.

For more on MATLAB build compilers, see MATLAB Build Compilers — Release 2009a.

### **Default Libraries**

EDA Simulator Link DS scripts fully support the use of default libraries.

The following table lists all the libraries shipped with the link software. The default libraries for each platform are in bold text.

| Platform            | MATLAB Library                                                                                            | Simulink Library                                                                                        |

|---------------------|-----------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------|

| Linux32,<br>Linux64 | liblfdhdlc_vlog_gcc336.so liblfdhdlc_mixed_gcc336.so liblfdhdlc_vlog_gcc412.so liblfdhldc_mixed_gcc412.so | liblfdhdlsvlog_gcc336.so liblfdhdlsmixed_gcc336.so liblfdhdls_vlog_gcc412.so liblfdhdls_mixed_gcc412.so |

### **Using an Alternative Library**

You can use a different HDL-side library by specifying it explicitly using the VG\_GNU\_PACKAGE properties of the launchDiscovery MATLAB command. You should choose the version of the library that matches the compiler and system libraries you are using for any other C/C++ libraries linked into the HDL simulator.

**Example: EDA Simulator Link DS Alternate Library Using launchDiscovery.** This example uses the GCC 4.1.2 compiler in the VG\_GNU\_PACKAGE.

```

'AccFile', 'mydesign.acc', ...

'UseDefaultVgGnuPackage', false, ...

'VgGnuGccVersion', 'gcc-4.1.2' ...

);

```

### **Starting the HDL Simulator**

### In this section...

"Starting the HDL Simulator from MATLAB" on page 1-15

"Starting the Synopsys VCS MX Software from a Shell" on page 1-16

### Starting the HDL Simulator from MATLAB

Start the Synopsy VCS MX simulator directly from MATLAB or Simulink by calling the MATLAB function launchDiscovery('PropertyName','PropertyValue'...). This function starts and configures the HDL simulator for use with the EDA Simulator Link DS software. By default, the function starts the first version of the simulator tools (vlogan, vhdlan, vcs)) that it finds on the system path (defined by the path variable), using a temporary file that is overwritten each time the HDL simulator starts.

**Note** If you want to start a different version of the simulator executable than the first one found on the system path, use the setenv and getenv MATLAB functions to set and get the environment of any sub-shells spawned by UNIX(), DOS(), or system().

To start the HDL simulator from MATLAB, enter launchDiscovery at the MATLAB command prompt:

```

>> launchDiscovery('property', 'value', ...)

```

You can customize the startup file and communication mode to be used between MATLAB or Simulink and the HDL simulator by specifying the call to launchDiscovery with property name/property value pairs. Refer to launchDiscovery reference documentation for specific information regarding the property name/property value pairs.

**Note** The launchDiscovery command requires the use of property name/property value pairs. You get an error if you try to use the function without them.

See "Example of Starting the Synopsys VCS MX Simulator from MATLAB" on page 1-16 for examples of using launchDiscovery with various property/name value pairs and other parameters.

When you specify a communication mode using launchDiscovery, the function applies the specified communication mode to all MATLAB or Simulink/HDL simulator sessions.

# Example of Starting the Synopsys VCS MX Simulator from MATLAB

This example compiles and launches a single-file HDL design for cosimulation with Simulink. The code allows the use of Verilog-2000 syntax in the HDL source. This code launches the Synopsys DVE software.

```

>> launchDiscovery( ...

'LinkType', 'Simulink', ...

'VerilogFiles', 'myinverter.v', ...

'VlogAnFlags', '+v2k', ...

'TopLevel', 'myinverter', ...

'AccFile', 'myinverter.acc' ...

);

```

### Starting the Synopsys VCS MX Software from a Shell

You can run the scripts generated with a call to launchDiscovery (or scripts you've created yourself) to start the Synopsys VCS MX software and load the link libraries outside of MATLAB. See launchDiscovery for more information and an example.

# Learning More About the EDA Simulator Link DS Software

### In this section...

"Documentation Overview" on page 1-17

"Online Help" on page 1-18

"Demos and Tutorials" on page 1-19

### **Documentation Overview**

The following documentation is available with this product.

| Chapter 1, "Getting Started"                                                           | Explains what the product is, the steps for installing and setting it up, how you might apply it to the hardware design process, and how to gain access to product documentation and online help. Directs you to product demos and tutorials.                                                      |

|----------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Chapter 2, "Simulating<br>an HDL Component in<br>a MATLAB Test Bench<br>Environment"   | Explains how to code HDL models and MATLAB test bench functions for EDA Simulator Link DS MATLAB applications. Provides details on how the link interface maps HDL data types to MATLAB data types and vice versa. Explains how to start and control HDL simulator and MATLAB test bench sessions. |

| Chapter 3, "Replacing an HDL Component with a MATLAB Component Function"               | Discusses the same topics as the chapter for test bench cosimulation using MATLAB software but instead using MATLAB to visualize an HDL module component.                                                                                                                                          |

| Chapter 4, "Simulating<br>an HDL Component in<br>a Simulink Test Bench<br>Environment" | Explains how to use the HDL simulator and Simulink for cosimulation modeling where Simulink acts as the test bench.                                                                                                                                                                                |

| Chapter 6, "Recording<br>Simulink Signal<br>State Transitions for<br>Post-Processing" | Provides instruction for adding a Value<br>Change Dump (VCD) file block to your<br>Simulink model for signal state change<br>capture.               |

|---------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------|

| Chapter 7, "Additional<br>Deployment Options"                                         | Contains several procedures for more complex cosimulation arrangements.                                                                             |

| Chapter 8, "Advanced<br>Operational Topics"                                           | Contains a variety of topics that provide a deeper understanding of how cosimulation works.                                                         |

| Chapter 9, "M-Function<br>Prototype Reference"                                        | Describes how to use the input and output arguments to an M-function created for use with the EDA Simulator Link DS commands matlabtb and matlabcp. |

| Chapter 10, "Functions — Alphabetical List"                                           | Describes EDA Simulator Link DS functions for use with MATLAB.                                                                                      |

| Chapter 11, "HDL Simulator<br>Command Extensions —<br>Alphabetical List"              | Describes EDA Simulator Link DS commands for use with the HDL simulator.                                                                            |

| Chapter 12, "Blocks —<br>Alphabetical List"                                           | Describes EDA Simulator Link DS blocks for use with Simulink.                                                                                       |

### **Online Help**

The following online help is available:

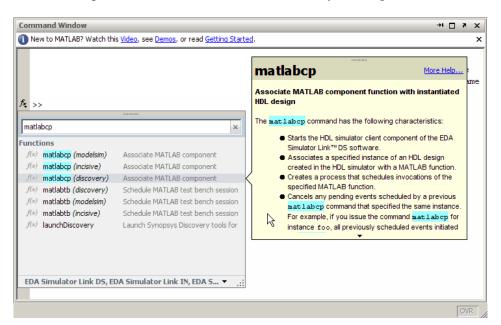

Online help in the MATLAB Help browser. Click the EDA Simulator Link DS product link in the browser's Contents or access using the MATLAB doc command at the MATLAB command prompt:

doc hdldaemon

M-help for EDA Simulator Link DS MATLAB functions and HDL simulator commands. This help is accessible with the MATLAB help command. For example, enter the command

help hdldaemon

at the MATLAB command prompt.

• Function help in the MATLAB command window by clicking the kicon:

• Block reference pages accessible through the Simulink interface.

### **Demos and Tutorials**

The EDA Simulator Link DS software provides demos and tutorials to help you get started.

The demos give you a quick view of the product's capabilities and examples of how you might apply the product. You can run them with limited product exposure. You can find the EDA Simulator Link DS demos with the online documentation. To access demos, type at the MATLAB command prompt:

>> demos

Select Links and Targets > EDA Simulator Link™ DS from the navigational pane.

# Simulating an HDL Component in a MATLAB Test Bench Environment

- "Workflow for Simulating an HDL Component with a MATLAB Test Bench Function" on page 2-2

- "Overview to Using MATLAB as a Test Bench" on page 2-5

- "Code HDL Modules for Verification Using MATLAB" on page 2-7

- "Code an EDA Simulator Link DS MATLAB Test Bench Function" on page 2-11

- "Place Test Bench Function on MATLAB Search Path" on page 2-20

- "Start hdldaemon to Provide Connection to HDL Simulator" on page 2-21

- "Launch HDL Simulator for Use with MATLAB" on page 2-23

- "Invoke matlabth to Bind and Schedule MATLAB Test Bench Function Calls" on page 2-24

- "Run MATLAB Test Bench Simulation" on page 2-29

- "Stop Test Bench Simulation" on page 2-33

### Workflow for Simulating an HDL Component with a **MATLAB Test Bench Function**

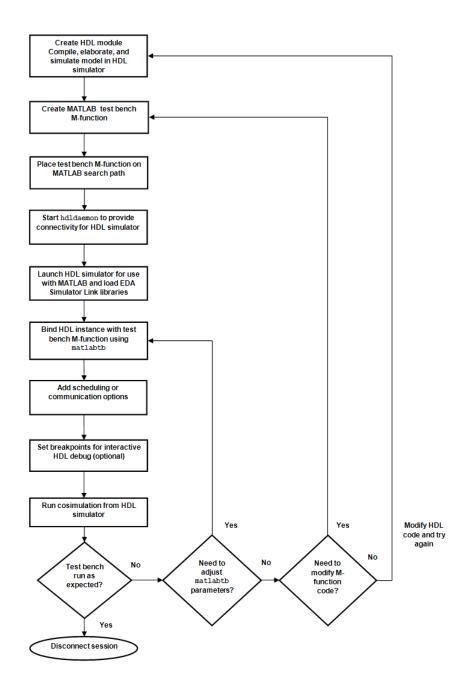

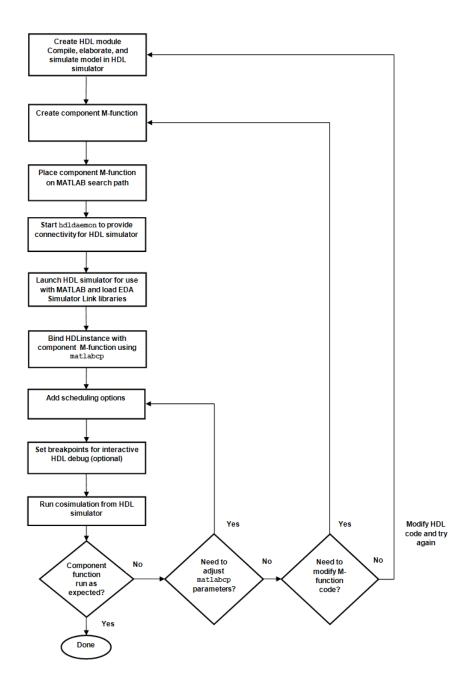

The following workflow shows the steps necessary to create a MATLAB test bench session for cosimulation with the HDL simulator using EDA Simulator Link DS.

### The workflow is as follows:

- Create HDL module. Compile, elaborate, and simulate model in HDL simulator.

- Create MATLAB test bench M-function.

- Place test bench function on MATLAB search path.

- Start hdldaemon to provide connection to HDL simulator.

- Launch HDL simulator for use with MATLAB and load EDA Simulator Link DS libraries.

- Bind HDL instance with test bench function.

- Add scheduling options.

- Set breakpoints for interactive HDL debug (optional).

- Run cosimulation from HDL simulator.

- End cosimulation session.

#### Overview to Using MATLAB as a Test Bench

The EDA Simulator Link DS software provides a means for verifying HDL modules within the MATLAB environment. You do so by coding an HDL model and a MATLAB M-function that can share data with the HDL model. This chapter discusses the programming, interfacing, and scheduling conventions for MATLAB test bench functions that communicate with the HDL simulator.

*MATLAB test bench* functions let you verify the performance of the HDL model, or of components within the model. A test bench function drives values onto signals connected to input ports of an HDL design under test and receives signal values from the output ports of the module.

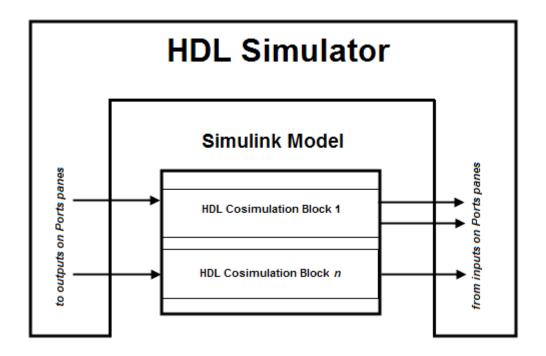

The following figure shows how a MATLAB M-function wraps around and communicates with the HDL simulator during a test bench simulation session.

# MATLAB MATLAB test bench M-Function Stimulus Response HDL Simulator HDL Entity Output Arguments

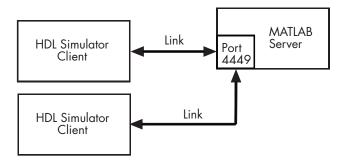

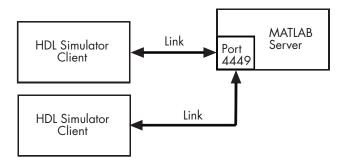

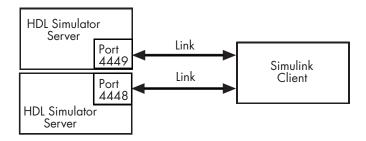

When linked with MATLAB, the HDL simulator functions as the client, with MATLAB as the server. The following figure shows a multiple-client scenario connecting to the server at TCP/IP socket port 4449.

The MATLAB server can service multiple simultaneous HDL simulator sessions and HDL modules. However, you should follow recommended guidelines to ensure the server can track the I/O associated with each module and session. The MATLAB server, which you start with the supplied MATLAB function hdldaemon, waits for connection requests from instances of the HDL simulator running on the same or different computers. When the server receives a request, it executes the specified MATLAB M-function you have coded to perform tasks on behalf of a module in your HDL design. Parameters that you specify when you start the server indicate whether the server establishes shared memory or TCP/IP socket communication links.

Refer to "Establishing EDA Simulator Link DS Machine Configuration Requirements" on page 7-8 for valid machine configurations.

**Note** The programming, interfacing, and scheduling conventions for test bench functions and component functions (see Chapter 3, "Replacing an HDL Component with a MATLAB Component Function") are virtually identical. Most of this chapter focuses on test bench functions, but in general all operations can be performed on and with both functions.

#### Code HDL Modules for Verification Using MATLAB

#### In this section...

"Overview to Coding HDL Modules for Use with MATLAB" on page 2-7

"Choosing an HDL Module Name" on page 2-7

"Specifying Port Direction Modes in HDL Components (MATLAB as Test Bench)" on page 2-8

"Specifying Port Data Types in HDL Components (MATLAB as Test Bench)" on page 2-8

"Sample VHDL Entity Definition" on page 2-10

"Compiling and Debugging the HDL Model" on page 2-10

# Overview to Coding HDL Modules for Use with MATLAB

The most basic element of communication in the EDA Simulator Link DS interface is the HDL module. The interface passes all data between the HDL simulator and MATLAB as port data. The EDA Simulator Link DS software works with any existing HDL module. However, when you code an HDL module that is targeted for MATLAB verification, you should consider its name, the types of data to be shared between the two environments, and the direction modes. The sections within this chapter cover these topics.

#### **Choosing an HDL Module Name**

Although not required, when naming the HDL module, consider choosing a name that also can be used as a MATLAB M-function name. (Generally, naming rules for VHDL or Verilog and MATLAB are compatible.) By default, EDA Simulator Link DS software assumes that an HDL module and its simulation function share the same name. See "Binding the HDL Module Component to the MATLAB Test Bench Function" on page 2-26.

For details on MATLAB function-naming guidelines, see "MATLAB Programming Tips" on files and file names in the MATLAB documentation.

# Specifying Port Direction Modes in HDL Components (MATLAB as Test Bench)

In your module statement, you must specify each port with a direction mode (input, output, or bidirectional). The following table defines these three modes.

| Use VHDL<br>Mode | Use Verilog<br>Mode | For Ports That                                                                                  |

|------------------|---------------------|-------------------------------------------------------------------------------------------------|

| IN               | input               | Represent signals that can be driven by a MATLAB function                                       |

| OUT              | output              | Represent signal values that are passed to a MATLAB function                                    |

| INOUT            | inout               | Represent bidirectional signals that can<br>be driven by or pass values to a MATLAB<br>function |

# Specifying Port Data Types in HDL Components (MATLAB as Test Bench)

This section describes how to specify data types compatible with MATLAB for ports in your HDL modules. For details on how the EDA Simulator Link DS interface converts data types for the MATLAB environment, see "Performing Data Type Conversions" on page 8-5.

**Note** If you use unsupported types, the EDA Simulator Link DS software issues a warning and ignores the port at run time. For example, if you define your interface with five ports, one of which is a VHDL access port, at run time, then the interface displays a warning and your M-code sees only four ports.

#### **Port Data Types for VHDL Entities**

In your entity statement, you must define each port that you plan to test with MATLAB with a VHDL data type that is supported by the EDA Simulator Link DS software. The interface can convert scalar and array data of the following VHDL types to comparable MATLAB types:

- STD\_LOGIC, STD\_ULOGIC, BIT, STD\_LOGIC\_VECTOR, STD\_ULOGIC\_VECTOR, and BIT VECTOR

- INTEGER and NATURAL

- REAL

- TIME

- Enumerated types, including user-defined enumerated types and CHARACTER

The interface also supports all subtypes and arrays of the preceding types.

**Note** The EDA Simulator Link DS software does not support VHDL extended identifiers for the following components:

- Port and signal names used in cosimulation

- Enum literals when used as array indices of port and signal names used in cosimulation

However, the software does support basic identifiers for VHDL.

#### **Port Data Types for Verilog Modules**

In your module definition, you must define each port that you plan to test with MATLAB with a Verilog port data type that is supported by the EDA Simulator Link DS software. The interface can convert data of the following Verilog port types to comparable MATLAB types:

- reg

- integer

- wire

**Note** EDA Simulator Link DS software does not support Verilog escaped identifiers for port and signal names used in cosimulation. However, it does support simple identifiers for Verilog.

#### **Sample VHDL Entity Definition**

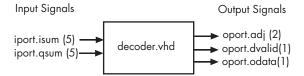

This sample VHDL code fragment defines the entity decoder. By default, the entity is associated with MATLAB test bench function decoder.

The keyword PORT marks the start of the entity's port clause, which defines two IN ports—isum and qsum—and three OUT ports—adj, dvalid, and odata. The output ports drive signals to MATLAB function input ports for processing. The input ports receive signals from the MATLAB function output ports.

Both input ports are defined as vectors consisting of five standard logic values. The output port adj is also defined as a standard logic vector, but consists of only two values. The output ports dvalid and odata are defined as scalar standard logic ports. For information on how the EDA Simulator Link DS interface converts data of standard logic scalar and array types for use in the MATLAB environment, see "Performing Data Type Conversions" on page 8-5.

```

ENTITY decoder IS

PORT (

isum : IN std_logic_vector(4 DOWNTO 0);

qsum : IN std_logic_vector(4 DOWNTO 0);

adj : OUT std_logic_vector(1 DOWNTO 0);

dvalid : OUT std_logic;

odata : OUT std_logic);

END decoder ;

```

#### Compiling and Debugging the HDL Model

After you create or edit your HDL source files, use the HDL simulator compiler to compile and debug the code.

For more examples, see the EDA Simulator Link DS tutorials. For details on using the HDL compiler, see the simulator documentation.

# Code an EDA Simulator Link DS MATLAB Test Bench Function

#### In this section...

"Process for Coding MATLAB EDA Simulator Link DS Functions" on page 2-11

"Syntax of a Test Bench Function" on page 2-12

"Sample MATLAB Test Bench Function" on page 2-12

## Process for Coding MATLAB EDA Simulator Link DS Functions

Coding a MATLAB M-function that is to verify an HDL module or component requires that you follow specific coding conventions. You must also understand the data type conversions that occur, and program data type conversions for operating on data and returning data to the HDL simulator.

To code a MATLAB function that is to verify an HDL module or component, perform the following steps:

- 1 Learn the syntax for a MATLAB EDA Simulator Link DS test bench function (see "Syntax of a Test Bench Function" on page 2-12.).

- **2** Understand how EDA Simulator Link DS software converts data from the HDL simulator for use in the MATLAB environment (see "Performing Data Type Conversions" on page 8-5in Chapter 8, "Advanced Operational Topics").

- **3** Choose a name for the MATLAB function (see "Binding the HDL Module Component to the MATLAB Test Bench Function" on page 2-26).

- **4** Define expected parameters in the function definition line (see "Defining EDA Simulator Link DS M-Functions and Function Parameters" on page 9-2in the Chapter 9, "M-Function Prototype Reference").

- **5** Determine the types of port data being passed into the function (see "Defining EDA Simulator Link DS M-Functions and Function Parameters" on page 9-2in the Chapter 9, "M-Function Prototype Reference").

- **6** Extract and, if appropriate for the simulation, apply information received in the portinfo structure (see "Gaining Access to and Applying Port Information" on page 9-5 in the Chapter 9, "M-Function Prototype Reference").

- **7** Convert data for manipulation in the MATLAB environment, as necessary (see "Converting HDL Data to Send to MATLAB" on page 8-5 in Chapter 8, "Advanced Operational Topics").

- **8** Convert data that needs to be returned to the HDL simulator (see "Converting Data for Return to the HDL Simulator" on page 8-10 in Chapter 8, "Advanced Operational Topics").

#### Syntax of a Test Bench Function

The syntax of a MATLAB test bench function is

```

function [iport, tnext] = MyFunctionName(oport, tnow, portinfo)

```

See the Chapter 9, "M-Function Prototype Reference" for an explanation of each of the function arguments.

#### Sample MATLAB Test Bench Function

This section uses a sample MATLAB function to identify sections of a MATLAB test bench function required by the EDA Simulator Link DS software. You can see the full text of the code used in this sample in the section MATLAB Function Example: manchester\_decoder.m on page 2-17.

As the first step to coding a MATLAB test bench function, you must understand how the data modeled in the VHDL entity maps to data in the MATLAB environment. The VHDL entity decoder is defined as follows:

```

ENTITY decoder IS

PORT (

isum : IN std_logic_vector(4 DOWNTO 0);

qsum : IN std_logic_vector(4 DOWNTO 0);

adj : OUT std_logic_vector(1 DOWNTO 0);

dvalid : OUT std_logic;

odata : OUT std_logic

);

```

```

END decoder;

```

The following discussion highlights key lines of code in the definition of the manchester decoder MATLAB function:

#### 1 Specify the MATLAB function name and required parameters.

The following code is the function declaration of the manchester\_decoder MATLAB function.

```

function [iport,tnext] = manchester decoder(oport,tnow,portinfo)

```

See "Defining EDA Simulator Link DS M-Functions and Function Parameters" on page 9-2 in the Chapter 9, "M-Function Prototype Reference".

The function declaration performs the following actions:

- Names the function. This declaration names the function manchester\_decoder, which differs from the entity name decoder. Because the names differ, the function name must be specified explicitly later when the entity is initialized for verification with the matlabtb or matlabtbeval HDL simulator command. See "Binding the HDL Module Component to the MATLAB Test Bench Function" on page 2-26.

- Defines required argument and return parameters. A MATLAB test bench function *must* return two parameters, iport and tnext, and pass three arguments, oport, tnow, and portinfo, and *must* appear in the order shown. See "Defining EDA Simulator Link DS M-Functions and Function Parameters" on page 9-2 in the Chapter 9, "M-Function Prototype Reference".

The function outputs must be initialized to empty values, as in the following code example:

```

tnext = [];

iport = struct();

```

You should initialize the function outputs at the beginning of the function, to follow recommended best practice.

The following figure shows the relationship between the entity's ports and the MATLAB function's iport and oport parameters.

For more information on the required MATLAB test bench function parameters, see "Defining EDA Simulator Link DS M-Functions and Function Parameters" on page 9-2 in the Chapter 9, "M-Function Prototype Reference".

#### 2 Make note of the data types of ports defined for the entity being simulated.

The EDA Simulator Link DS software converts HDL data types to comparable MATLAB data types and vice versa. As you develop your MATLAB function, you must know the types of the data that it receives from the HDL simulator and needs to return to the HDL simulator.

The VHDL entity defined for this example consists of the following ports

#### **VHDL Example Port Definitions**

| Port | Direction | Туре                         | Converts<br>to/Requires<br>Conversion to                                                                             |

|------|-----------|------------------------------|----------------------------------------------------------------------------------------------------------------------|

| isum | IN        | STD_LOGIC_VECTOR(4 DOWNTO 0) | A 5-bit column<br>or row vector of<br>characters where<br>each bit maps to<br>a standard logic<br>character literal. |

| qsum | IN        | STD_LOGIC_VECTOR(4 DOWNTO 0) | A 5-bit column<br>or row vector of<br>characters where<br>each bit maps to<br>a standard logic<br>character literal. |

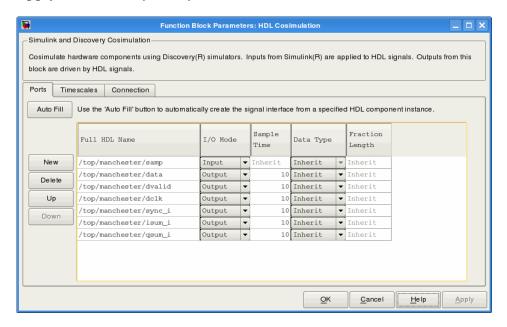

#### **VHDL Example Port Definitions (Continued)**